# Informatik IModul 4: Schaltwerke

© 2010 Burkhard Stiller

M4 - 1

### **Modul 4: Schaltwerke**

- Formale Grundlagen

- Endliche Automaten

- Asynchrone Schaltwerke, Flip-Flops

- Synchrone Schaltwerke

- □ Register-Transfer-Ebene

- □ Spezielle Schaltwerke

- Register, Zähler, Schieberegister

ifi

#### **Schaltwerke**

- Schaltnetze (kombinatorische Schaltungen):

- Die Ausgabe hängt lediglich von den Werten der Eingangsvariablen zum gleichen Zeitpunkt ab.

- Für diese Unterscheidung seien Laufzeitverzögerungen vernachlässigt!

- Schaltwerke (sequentielle Schaltungen):

- Die Ausgabewerte hängen auch von Belegungen der Eingangsvariablen zu vergangenen Zeitpunkten ab.

© 2010 Burkhard Stiller

M4 - 3

### **Schaltwerke**

- Man faßt alle Abhängigkeiten von Werten der Vergangenheit in einem sogenannten Zustand zusammen.

- Das Schaltwerk erzeugt damit seine Ausgabe in Abhängigkeit von den augenblicklichen Eingangsvariablen und seinem Zustand; diese Größen beeinflussen auch den nächsten Zustand des Schaltwerks.

- Man kann Schaltwerke als Implementierungen von deterministischen endlichen Automaten interpretieren.

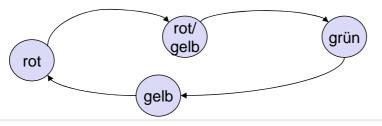

Zustände einer Ampel

# Einführung in die Automatentheorie

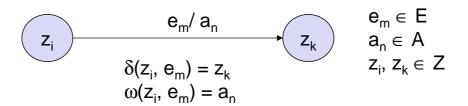

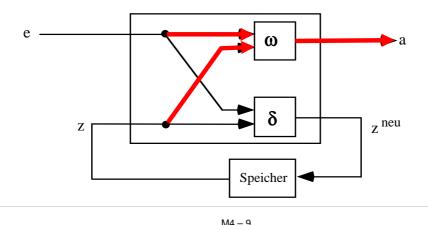

- □ Ein 6-Tupel M = (E, A, Z, δ, ω,  $z_0$ ) heißt Automat, wenn E, A und Z nichtleere Mengen sind

- E ist die Menge der Eingangsbelegungen e,

- A die Menge der Ausgangsbelegungen a und

- Z die Menge der Zustände z.

- □ Überführungsfunktion  $\delta: Z \times E \rightarrow Z$

- $\square$   $\delta$  ist eine auf der Menge  $Z \times E$  definierte Funktion, deren Werte in Z liegen.

- □ Ausgabefunktion  $\omega$ : Z × E  $\rightarrow$  A

- $oldsymbol{\square}$   $\omega$  eine auf der Menge  $Z \times E$  definierte Funktion, deren Werte in A liegen.

- Grundzustand z<sub>0</sub>

© 2010 Burkhard Stiller

M4 – 5

#### <u>ifi</u>

# **Beispiel**

Allgemein:

Ampel (nicht vollständig spezifiziert)

Auto auf Kontaktschleife /

Starte Wartezeit rot/gelb

rot

gelb

E = {Auto auf Kontaktschleife, Fußgängertaste gedrückt, ...}

A = {Starte Wartezeit rot/gelb, Starte Summer, ...}

Z = {rot, rot/gelb, grün, gelb}

$\delta$ (rot, Auto auf Kontaktschleife) = rot/gelb  $\omega$ (rot, Auto auf Kontaktschleife) = Starte Wartezeit rot/gelb

# Einführung in die Automatentheorie

- □ Die Zustandsmenge Z ermöglicht die Speicherung von Wissen über Eingangsbelegungen der Vergangenheit.

- □ Die aktuelle Ausgabebelegung wird durch die Funktion ω, der neue Zustand durch die Funktion δ aus den aktuellen Eingangsbelegungen und dem alten Zustand erzeugt.

© 2010 Burkhard Stiller

M4 – 7

#### ifi

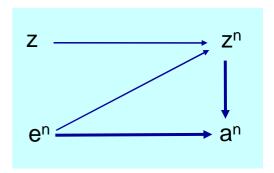

# **Mealy- und Moore-Automat (1)**

□ Hängt der Ausgabewert lediglich vom augenblicklichen Zustand ab, spricht man in diesem Falle von einem Moore-Automaten oder Moore-Schaltwerk.

$$a = \omega(z)$$

$a \in A;$

$$z^{\text{neu}} = \delta (z,e)$$

$e \in E$ ;

$$z, z^{neu} \in Z$$

# **Mealy- und Moore-Automat (2)**

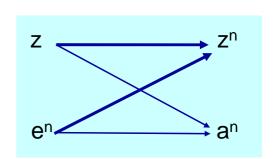

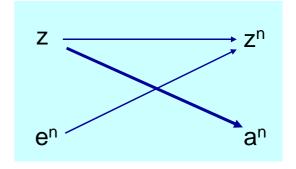

Geht auch die Eingabebelegung in die Berechnung des Ausgabewertes ein, erhält man in diesem Falle einen Mealy-Automaten oder Mealy-Schaltwerk.

$$\begin{array}{ll} \underline{a} = \omega \, (z,e) & z^{\text{neu}} = \, \delta \, (z,e) \\ \underline{e} \in \, E; & a \in \, A; & z, \, z^{\text{neu}} \in \, Z \end{array}$$

© 2010 Burkhard Stiller

#### ifi

# Verhaltensunterschied dieser Automaten (1)

- Mealy-Automat:

- Ausgabewerte können sich sofort mit der Änderung von Eingabevariablen ändern.

- □ Mealy-Automat 1. Art:

- Es wird zunächst aus der neu anliegenden Eingabebelegung die Ausgabebelegung gebildet und dann in den Folgezustand gewechselt.

- Anwendung: synchrone Schaltwerke

# Verhaltensunterschied dieser Automaten (2)

- Mealy-Automat 2. Art:

- Es wird zunächst aus der neu anliegenden Eingabebelegung der Folgezustand und dann mit der noch anliegenden Eingabebelegung die Ausgabebelegung gebildet.

- □ Anwendung: asynchrone Schaltwerke

© 2010 Burkhard Stiller

M4 - 11

# Verhaltensunterschied dieser Automaten (3)

- Moore-Automat:

- Die Ausgabebelegung ist unabhängig von der Eingabebelegung, sie kann sich nur nach einem Zustandswechsel ändern.

- Anwendung: synchrone und asynchrone Schaltwerke

## Darstellungsmöglichkeiten (1)

- □ Beim Entwurf eines Automaten liegt die Aufgabenstellung zunächst in einer informalen globalen Form vor z.B. durch:

- Pflichtenheft:

Beschreibt verbal, was die zu entwerfende Schaltung leisten soll.

- Weitere Pläne:

Ablaufpläne, Technologiebeschreibung, usw. zur Ergänzung der verbalen Beschreibung

- □ Für einen systematischen und ggf. rechnergestützten Entwurf ist ein Übergang zu einer formalisierten Beschreibung, die das Sollverhalten ausreichend spezifiziert, notwendig.

© 2010 Burkhard Stiller

M4 - 13

# Darstellungsmöglichkeiten (2)

- Vier unterschiedliche Möglichkeiten zur formalisierten

Beschreibung des Verhaltens eines Automaten sollen an einem Beispiel demonstriert werden:

- Beispiel:

- Durch ein Schaltwerk soll eine einlaufende Impulsfolge am Eingang x derart verarbeitet werden, daß die Eingangsimpulse x abwechselnd an den beiden Ausgängen y<sub>0</sub> und y<sub>1</sub> erscheinen.

- Gesucht ist eine formalisierte Beschreibung dieses Problems.

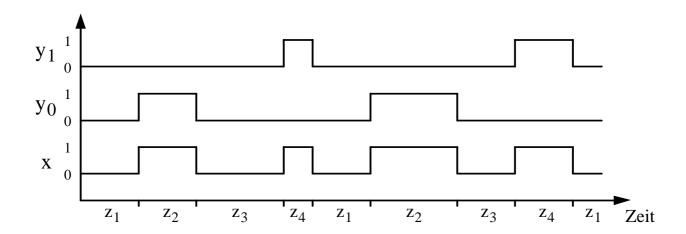

# 1. Zeitdiagramm

- □ Dient zur Veranschaulichung des Problems.

- Es wird eine beispielhafte Folge von Eingabebelegungen dargestellt.

© 2010 Burkhard Stiller

M4 - 15

#### ifi

# 1. Zeitdiagramm

- $z_1$  = Ausgabe von  $y_0y_1$  = 00 und warten auf x = 1 zur Ausgabe an Ausgang  $y_0$

- $z_2$  = Ausgabe von  $y_0y_1$  = 10 und warten auf x = 0

- $z_3$  = Ausgabe von  $y_0y_1$  = 00 und warten auf x = 1 zur Ausgabe an Ausgang  $y_1$

- $z_4 = Ausgabe von y_0 y_1 = 01 und warten auf x = 0$

#### 2. Ablauftabelle

Sind die Zustände bekannt, so kann die Überführungsfunktion  $z_{k+1} = \delta(z_k, x)$  und die Ausgabefunktion  $(y_0, y_1) = \omega(z_k, x)$  in einer Ablauftabelle dargestellt werden.

|                                  |                       | •                                |                                       |

|----------------------------------|-----------------------|----------------------------------|---------------------------------------|

| $\mathbf{Z}_{\mathbf{k}}$        | X                     | $z_{k+1}$                        | $y_0 y_1$                             |

| $\overline{z_1}$                 | 0                     | $\mathbf{z}_1$                   | 0 0                                   |

| $\mathbf{z}_1$                   | 1                     | $\mathbf{z}_2$                   | 1 0                                   |

| $\mathbf{z}_2$                   | 1                     | $\mathbf{z}_2$                   | 10                                    |

| $\mathbf{z}_2$                   | 0                     | $\mathbf{z}_3$                   | 0 0                                   |

| $\mathbf{z}_3$                   | 0                     | $\mathbf{Z}_3$                   | 0 0                                   |

| $\mathbf{z}_3$                   | 1                     | $\mathbf{z}_4$                   | 0 1                                   |

| $\mathbf{z}_4$                   | 1                     | $\mathbf{Z}_4$                   | 0 1                                   |

| $\mathbf{Z}_4$                   | 0                     | $z_1$                            | 0 0                                   |

| Start-<br>zustand z <sub>k</sub> | Eingangs-<br>belegung | Folge-<br>zustand z <sub>k</sub> | Ausgangs-<br><sub>+1</sub> belegungen |

© 2010 Burkhard Stiller

M4 – 17

ifi

### 3. Automatentabelle

- □ Andere Darstellungsform desselben Sachverhalts:

- In senkrechter Richtung: die Zustände.

- In waagerechter Richtung: die Eingangsbelegungen.

- In der Matrix: die Folgezustände.

| $\mathbf{z}_{\mathbf{k}}$ | $\mathbf{Z}_{k+1}$           | $y_0 y_1$ |

|---------------------------|------------------------------|-----------|

|                           | x=0 x=1                      |           |

| $\mathbf{z}_1$            | $\mathbf{z}_1  \mathbf{z}_2$ | 0.0       |

| $\mathbf{z}_2$            | $z_3$ $z_2$                  | 10        |

| $\mathbf{z}_3$            | $z_3$ $z_4$                  | 0.0       |

| $\mathbf{z}_4$            | $z_1$ $z_4$                  | 0.1       |

Moore-Automat

| $\mathbf{z}_{\mathbf{k}}$ | $z_{k+1}/y$        | $y_0 y_1$  |

|---------------------------|--------------------|------------|

|                           | x=0                | x=1        |

| $\mathbf{z}_1$            | z <sub>1</sub> /00 | $z_{2}/10$ |

| $\mathbf{z}_2$            | $z_{3}/00$         | $z_{2}/10$ |

| $z_3$                     | $z_{3}/00$         | $z_4/01$   |

| $\mathbf{z}_4$            | $z_{1}/00$         | $z_4/01$   |

Mealy-Automat

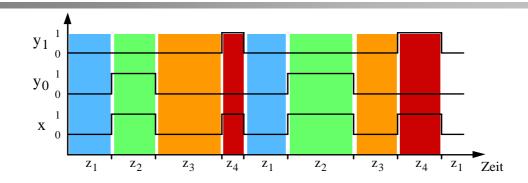

## 4. Automatengraph

- □ Die Überführungs- und Ausgabefunktionen werden in einem gerichteten Graphen AG = (Z,K) dargestellt, wobei Z die Menge der Zustände z und K die Menge der Übergänge k zwischen den Zuständen ist.

- □ Die Eingabebelegungen werden an die Kanten der zugehörigen Zustandsübergänge geschrieben.

© 2010 Burkhard Stiller

M4 – 19

#### ifi

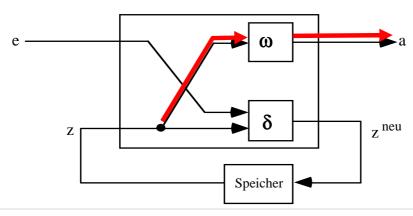

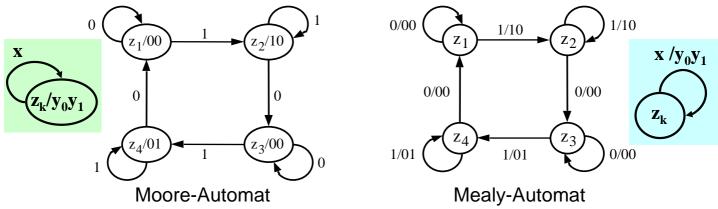

# Realisierung von Automaten

- Zur Speicherung vergangener Informationen ist ein Zustandsspeicher erforderlich.

- □ Einfachste Form dieses Zustandsspeichers:

- Rückkopplung

- Durch die Rückkopplung lassen sich die in den Eingangsvariablen nicht mehr repräsentierten Informationen wieder am Eingang zur Verfügung stellen.

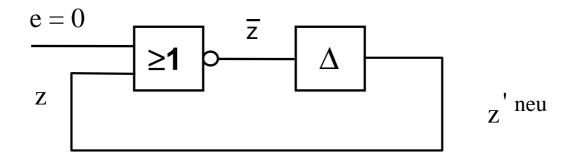

## Beispiel: Rückgekoppeltes NOR-Gatter

Als ideales Gatter betrachtet, ist die Schaltung unzulässig, denn es müßte gleichzeitig gelten:

$$z^{\text{neu}} = \overline{z}$$

und  $z = z^{\text{neu}}$

© 2010 Burkhard Stiller

M4 - 21

# Rückgekoppeltes NOR-Gatter

In der Realität hat jede Schaltung hat eine Verzögerungszeit größer 0 (Totzeitmodell).

Mit dieser Verzögerung erhält man:

$$z'^{\text{neu}}(t+\Delta) = z(t)$$

$z(t+\Delta) = z'^{\text{neu}}(t+\Delta)$

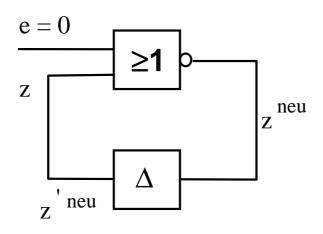

## Rückgekoppeltes NOR-Gatter

Zeichnet man die Schaltung etwas anders, so sieht man, daß das  $\Delta$ -Verzögerungsglied dem Speicher entspricht.

© 2010 Burkhard Stiller

M4 - 23

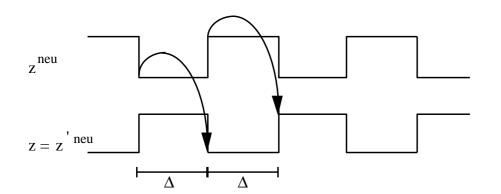

## Rückgekoppeltes NOR-Gatter

Das Zeitverhalten dieser Schaltung im Zeitdiagramm:

Das Verhalten der Schaltung ist stark von den Verzögerungszeiten abhängig.

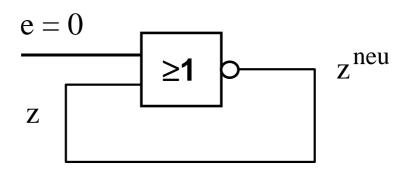

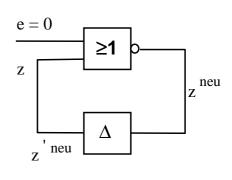

## Rückgekoppeltes NOR-Gatter

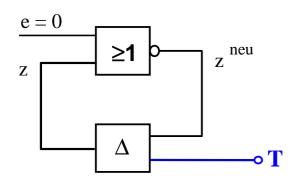

- Wie kann man ein von den Verzögerungszeiten unabhängiges Verhalten erreichen?

- Der Speicher wird so aufgebaut, daß z seinen alten

Wert so lange beibehält, bis z explizit durch ein externes Signal T auf z<sup>neu</sup> gesetzt wird.

#### **Beispiel:**

z behält seinen Wert solange, bis T von 0 auf 1 wechselt.

Dann wird z auf z<sup>neu</sup> gesetzt und behält diesen Wert bis zum nächsten 01-Wechsel von T.

© 2010 Burkhard Stiller

M4 - 25

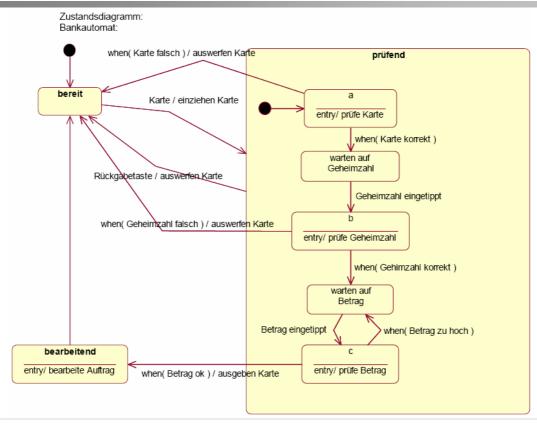

# **Automatengraph (Bancomat)**

## Automatengraph (Zustandsübergangsdiagramm)

#### Modul 4: Schaltwerke

- Formale Grundlagen

- Endliche Automaten

- Asynchrone Schaltwerke, Flip-Flops

- Synchrone Schaltwerke

- Register-Transfer-Ebene

- Spezielle Schaltwerke

- Register, Zähler, Schieberegister

#### **Definitionen**

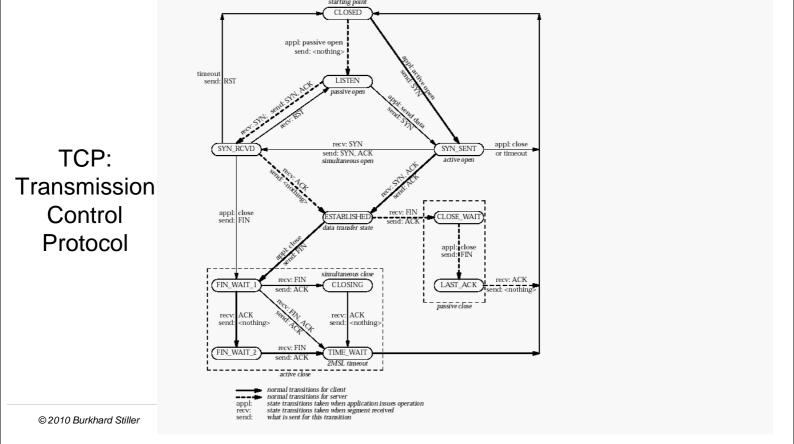

- Werden alle Zustandsspeicher von einem oder mehreren zentralen Synchronisationssignal(en) T (Takt) gesteuert, so spricht man von einem synchronen Schaltwerk.

- Anderenfalls spricht man von einem asynchronen Schaltwerk.

- Die Synchronisation über einen Takt kann flankengesteuert und pegelgesteuert sein

© 2010 Burkhard Stiller

M4 - 29

#### <u>ifi</u>

## **Pegelsteuerung**

- Der Speicher ist während einer Takthälfte transparent, während der anderen speichert er.

- Die Eingänge wirken sich nur auf den Zustand aus, wenn der Takt z.B. den Wert 1 hat. Ist der Takt 0, wird der Zustand gespeichert.

- Nachteil: Die Eingangssignale k\u00f6nnen sich w\u00e4hrend der aktiven (transparenten) Taktperiode mehrfach \u00e4ndern.

- □ Einfachste Realisierung: Konjunktive Verknüpfung jeder Eingangsvariablen mit dem Takt.

- Pegelgesteuerte Zustandsspeicher werden auch Latches genannt.

## **Flankensteuerung**

□ Nur während der positiven (0 → 1) oder der negativen (1 → 0) Taktflanke werden die Eingabewerte in den Speicher übernommen.

#### Vorteil:

Eingänge müssen nur für eine sehr kurze Zeitspanne gültig sein (und nicht über eine ganze Takthälfte wie bei der Pegelsteuerung).

⇒ die Auswertezeitpunkte sind exakter definiert

Schaltsymbol für einen flankengesteuerten Takteingang

© 2010 Burkhard Stiller M4 – 31

#### <u>ifi</u>

# Synchrone Schaltwerke vs. Asynchrone Schaltwerke (1)

- Synchrone Schaltwerke:

- Mittlere und größere Schaltwerke werden fast immer als synchrone Schaltwerke entworfen.

- □ Vorteil:

- Leichter zu analysieren und zu entwerfen als asynchrone Schaltwerke.

- □ Grund:

- Synchrone Schaltwerke sind unabhängig von (teilweise fertigungsabhängigen)

Verzögerungszeiten.

# Synchrone Schaltwerke vs. Asynchrone Schaltwerke (2)

- Wird die Dauer des Taktes nur größer als die maximale Verzögerungszeit im Schaltnetz gewählt:

- $\Rightarrow$  Die Ausgänge der Schaltnetze  $\delta$  und  $\omega$  haben sich stabilisiert, bevor sie sich auf  $z^{neu}$  auswirken.

- $\Rightarrow$  Zur Analyse und Synthese eines synchronen Schaltwerks muß man lediglich die Schaltnetze  $\delta$  und  $\omega$  betrachten.

- Die Schaltung kann an den Stellen aufgetrennt werden, an denen die Speicherelemente sitzen.

© 2010 Burkhard Stiller

M4 - 33

# Synchrone Schaltwerke vs. Asynchrone Schaltwerke (3)

- Asynchrone Schaltwerke:

- Der Entwurf asynchroner Schaltwerke ist aus zwei Gründen von Bedeutung:

- Die in synchronen Schaltwerken benutzten Speicherbausteine sind selbst kleine asynchrone Schaltwerke.

- Immer schneller werdende Bausteine zwingen zu teilweise asynchronen Entwurfstechniken.

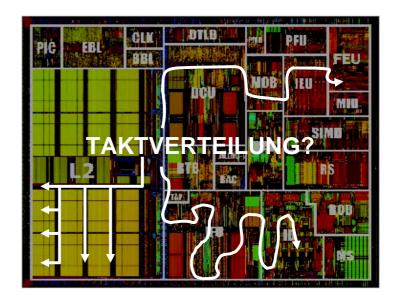

#### Warum?

# Synchrone Schaltwerke vs. Asynchrone Schaltwerke (4)

#### □ Begründung:

- Werden die Verzögerungszeiten der verwendeten Bausteine kleiner als die Signallaufzeiten auf der Schaltungsplatine/auf dem Chip (ca. 20-30 cm/ns)

- ⇒ dann ist der Takt ist nicht länger synchron, da er die einzelnen Bausteine je nach Entfernung zu für die Bausteine unterschiedlichen wahrnehmbaren Zeitpunkten erreicht!

1 GHz Takt = 1 ns Taktdauer!

© 2010 Burkhard Stiller

M4 - 35

#### ifi

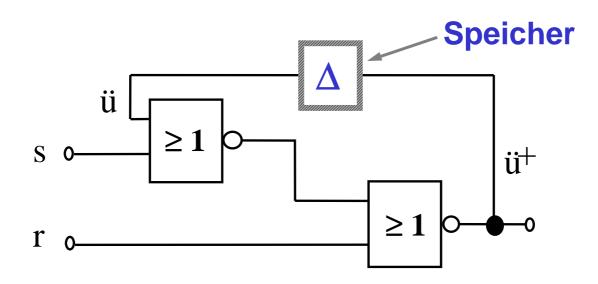

# Schaltbild des Speichers

Übergangsgleichung:  $\ddot{\mathbf{u}}^+ = \overline{\mathbf{r} \vee \overline{\ddot{\mathbf{u}} \vee \mathbf{s}}} = \overline{\mathbf{r}} (\ddot{\mathbf{u}} \vee \mathbf{s})$

Ausgangsgleichung:  $q = \ddot{u}$

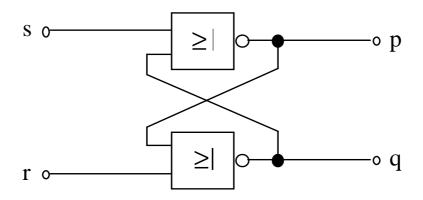

## **Asynchrones RS-Flipflop**

#### Dieser Speicher ist ein Standardelement.

- Es wird als asynchrones RS-Flipflop (bistabile Kippstufe) bezeichnet.

- Es wird üblicherweise nur etwas anders gezeichnet:

- Der zusätzliche Ausgang p ist im allgemeinen komplementär zu q, solange r und s nicht gleichzeitig 1 sind:  $\mathbf{p} = \overline{\mathbf{q}}$

- Nur für die beim Entwurf ausgesparte (und damit verbotene)

Eingabebelegung (r, s) = (1, 1) ist p = q = 0

© 2010 Burkhard Stiller

M4 - 37

## **Probleme asynchroner Schaltwerke**

#### □ Asynchrone Schaltwerke arbeiten ohne einen zentralen Takt:

- Sie reagieren sofort auf jede Änderung der Eingangs- und Zustandsvariablen.

- Sie sind sehr störempfindlich

#### Wettläufe von Zustandsvariablen:

- Diese verursachen falsche Zustandsübergänge

- Abhilfe: Wettlauffreie Zustandskodierung

## Hasardfehler in den Übergangs-Schaltnetzen:

- Hierauf reagieren asynchrone Schaltwerke naturgemäß sehr empfindlich.

Hasardfehler können ebenfalls falsche Zustandsübergänge und Oszillationen verursachen

- Abhilfe: Entwurf hasardarmer Schaltnetze für die Übergangs- und Ausgabefunktionen.

## **Probleme asynchroner Schaltwerke**

Zur weiteren Verringerung des Störrisikos arbeiten asynchrone Schaltwerke darüber hinaus meist im sogenannten

#### normal fundamental mode.

- Hierbei darf sich maximal eine Eingangsvariable gleichzeitig ändern.

- □ Ein Eingabewechsel kann erst dann erfolgen, wenn alle internen Änderungen abgeklungen sind.

© 2010 Burkhard Stiller

M4 - 39

#### <u>ifi</u>

# Wiederholung

- Schaltnetze: Ausgabe hängt nur von Eingangssignalen ab (kombinatorische Schaltungen, combinational circuits)

- Schaltwerke: Ausgabe kann auch von internen Zustand abhängen (sequentielle Schaltungen, sequential circuits)

- Synchrones Schaltwerk: Zustandsspeicher ist taktgesteuert, andernfalls asynchron

# Flipflops als Zustandsspeicher

- □ Die Probleme asynchroner Schaltwerke treten bei synchronen Schaltwerken nicht auf.

- Da alle Zustandsspeicher bei synchronen Schaltwerken durch einen zentralen Takt gesteuert werden, können sich alle Übergänge und die damit verbundenen Wettläufe stabilisieren, bevor der neue Zustand eingenommen wird.

- Synchrone Schaltwerke benötigen taktgesteuerte Zustandspeicher

- □ Hierfür werden Flipflops verwendet.

- □ Es existieren eine Reihe verschiedener Flipflop-Typen.

© 2010 Burkhard Stiller

M4 - 41

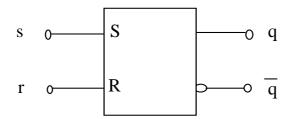

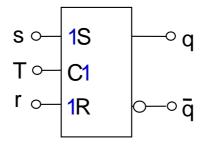

# **RS-Flipflop**

- □ Verhalten (RS-Flipflop):

- Eingang s soll den Speicher setzen (s=1 ⇒ Ausgang q=1)

- Eingang r soll den Speicher rücksetzen (r=1) ⇒ q=0)

- Speichern: r und s beide  $0 \Rightarrow q$  behält letzten Wert

- Verboten: r und s gleichzeitig 1  $\Rightarrow$  die Ausgänge p und q sind komplementär

- Die Zustandsvariable q und ihre Negation  $\overline{q}$  (= p) stehen am Ausgang zur Verfügung.

- □ Schaltsymbol des asynchronen RS-Flipflops:

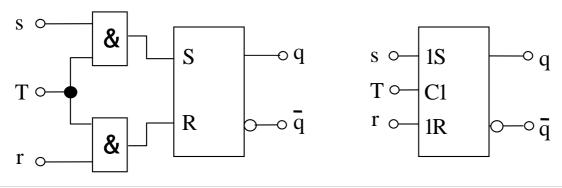

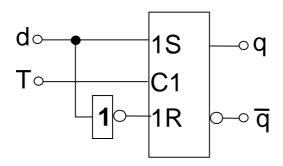

# RS-Flipflop → pegelgesteuertes RS-Latch

- Um das RS-Flipflop in einem synchronen Schaltwerk verwenden zu können:

- Taktsignal muß eingeführt werden, welches die Änderung der Zustandsvariablen in der inaktiven Taktphase verhindert.

- Dies ist leicht zu erreichen, indem man die beiden Eingänge durch je ein UND-Gatter mit diesem Takt verknüpft:

- □ Wir erhalten das pegelgesteuerte RS-Latch

© 2010 Burkhard Stiller

M4 - 43

#### <u>ifi</u>

# **Anmerkung zur Notation**

- □ Die Ziffer 1 bei den Eingängen (1S, 1R) bedeutet, daß sie in ihrer Wirksamkeit von dem ebenfalls mit 1 gekennzeichneten Takt C1 abhängen.

- Verursacht ein Eingang die Abhängigkeit, so folgt die Ziffer der Eingangsvariablen, anderenfalls geht sie voraus.

# **Ansteuertabelle (RS-Flipflop)**

- Beim Entwurf synchroner Schaltwerke sind Zustand und gewünschter Folgezustand bekannt.

- Gesucht sind die Werte der Ansteuervariablen der Flipflops.

- □ Diese lassen sich leicht mit Hilfe der sog. Ansteuertabelle eines Flipflops bestimmen.

- Die Ansteuertabelle gibt den Zustandsübergang eines Flipflops unter den verschiedenen Eingabebelegungen wieder.

- Sie läßt sich i.a. auf einfache Weise aus der Funktionstabelle der Ausgabe- und Übergangsfunktionen gewinnen.

© 2010 Burkhard Stiller

M4 - 45

# **Ansteuertabelle (RS-Flipflop)**

Ansteuertabelle des asynchronen RS-Flipflops:

| $q^{t}$ | q <sup>t+1</sup> | r | S |            |

|---------|------------------|---|---|------------|

| 0       | 0                | ı | 0 | Halten     |

| 0       | 1                | 0 | 1 | Setzen     |

| 1       | 0                | 1 | 0 | Rücksetzen |

| 1       | 1                | 0 | - | Halten     |

#### Voraussetzung:

Es dürfen keine unerlaubten Eingangsbelegungen auftreten.

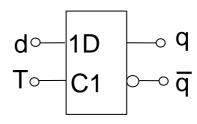

# **D-Flipflop**

- □ Bei einem RS-Flipflop ist stets die Nebenbedingung ( $r \land s = 0$ ) zu beachten.

- Führt man eine Eingangsvariable d bejaht zum S-Eingang und negiert zum R-Eingang, ist diese Bedingung stets erfüllt.

- □ Damit erhält man ein sogenanntes D-Latch.

© 2010 Burkhard Stiller

M4 - 47

#### <u>ifi</u>

## Verhalten des D-Flipflops

#### Verhalten:

- Der anliegende Eingabewert wird in allen Fällen als Flipflopzustand übernommen und einen Takt lang gespeichert.

- Das Eingangssignal wird um eine Taktperiode verzögert am Ausgang zur Verfügung gestellt.

- □ Daher der Name D-Latch von "to delay" = verzögern

|                   | d | qt | q <sup>t+1</sup> |

|-------------------|---|----|------------------|

|                   | 0 | 0  | 0                |

| Funktionstabelle: | 0 | 1  | 0                |

|                   | 1 | 0  | 1                |

|                   | 1 | 1  | 1                |

#### Ansteuertabelle des D-Latch

| qt | q <sup>t+1</sup> | d | d | qt | q <sup>t+1</sup> |

|----|------------------|---|---|----|------------------|

| 0  | 0                | 0 |   | 0  |                  |

| 0  | 1                | 1 | 0 | 1  |                  |

| 1  | 0                | 0 | 1 | _  | -                |

| 1  | 1                | 1 | 1 | 1  | 1                |

Leicht aus der Funktionstabelle durch Permutieren der Spalten gewinnbar.

© 2010 Burkhard Stiller

M4 - 49

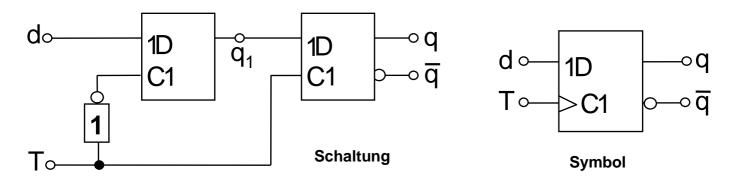

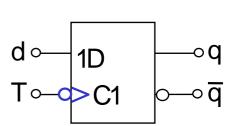

# Taktflankengesteuertes D-Flipflop

- Ein taktflankengesteuertes D-Flipflop erhält man durch die Zusammenschaltung zweier D-Latches, die mit komplementären Taktpegeln gesteuert werden.

- Das erste Latch wird Master-Latch, das zweite Slave-Latch genannt.

- □ Ein solches Flipflop wird auch als Master-Slave-Flipflop bezeichnet.

#### **Funktionsweise**

- Während T = 0 folgt das erste Latch den Änderungen des Eingangssignals d, während das zweite Latch verriegelt ist.

- Ändert sich T von 0 auf 1 (positive Taktflanke), wird das erste Flipflop verriegelt.

- Unabhängig von den nun auftretenden Änderungen von d bleibt der Ausgabewert

q<sub>1</sub> gleich dem Wert von d, der beim 0-1-Wechsel des Taktes anlag.

- Dieser Wert wird in das zweite Latch übernommen und dort auch weiter gespeichert, wenn T wieder auf 0 zurückgeht.

© 2010 Burkhard Stiller

M4 - 51

#### <u>ifi</u>

# **Anmerkungen**

- D-Flipflops sind die am einfachsten zu realisierenden flankengesteuerten Speicherelemente.

- Sie sind wegen des geringen Flächenbedarfs die in integrierten Schaltungen am häufigsten verwendeten Speicherglieder.

- Im Schaltsymbol wird die Taktflankensteuerung durch ein Dreieck am Takteingang spezifiziert.

- Bei einer Steuerung mit der negativen Taktflanke wird ein Negationszeichen vor das Dreieck gesetzt.

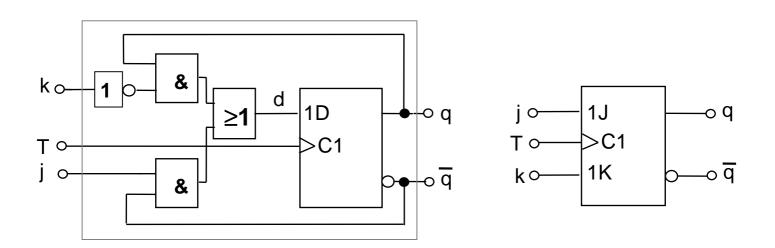

# **JK-Flipflop**

- $\Box$  Beim RS-Flipflop war die Eingangsvariablen-Kombination r = s = 1 verboten

- □ Ziel: Ein Flipflop entwerfen, welches diese Kombination nutzt.

- □ Als vierte Funktion neben "speichern", "setzen" und "rücksetzen" soll bei Eingangskombination r = s = 1 der Flipflop-Inhalt komplementiert werden.

- Bezeichnung:

- j: resultierender Setzeingang

- k: resultierender Rücksetzeingang

Dieses Verhalten läßt sich durch Zusatzbeschaltung schon bekannter Flipflops erreichen.

© 2010 Burkhard Stiller

M4 - 53

#### <u>ifi</u>

## Schaltbild des synchronen JK-Flipflops

$$d = q^t \overline{k} \vee \overline{q}^t j$$

# Funktions-/Ansteuertabelle des JK-Flipflops

| Verkürzte Funktionstabelle                   | j                | k                | q <sup>t+1</sup> | Funktion   |

|----------------------------------------------|------------------|------------------|------------------|------------|

| des JK-Flipflops:                            | 0                | 0                | qt               | speichern  |

|                                              | 0                | 1                | 0                | rücksetzen |

|                                              | 1                | 0                | 1_               | setzen     |

|                                              | 1                | 1                | qt               | wechseln   |

|                                              |                  |                  |                  |            |

|                                              | $\mathbf{q}^{t}$ | q <sup>t+1</sup> | j                | k          |

| Aus obiger Tabelle läßt sich auch leicht die | 0                | 0                | 0                | -          |

| Ansteuertabelle des                          | 0                | 1                | 1                | -          |

| JK-Flipflops gewinnen:                       | 1                | 0                | _                | 1          |

|                                              | 1                | 1                | _                | 0          |

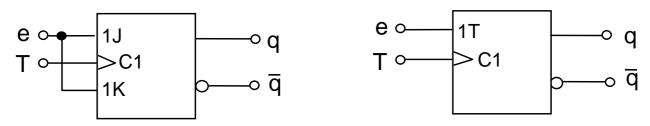

# **Das T-Flipflop**

M4 - 55

- □ Ein T-Flipflop ("to toggle", kippen) hat nur einen Eingang.

- □ Liegt an diesem Eingang eine "1", kippt das Flipflop mit jedem Taktimpuls in einen anderen Zustand, hat die Eingangsvariable den Wert "0", behält das Flipflop seinen alten Zustand bei.

- Durch geeignete Eingangsbeschaltung eines JK-Flipflops läßt sich leicht das Verhalten eines T-Flipflops erzeugen.

Synchrones T-Flipflop

ifi

© 2010 Burkhard Stiller

## T-Flipflop: Verkürzte Funktionstabelle

Verkürzte Funktionstabelle des T-Flipflops

| е | q <sup>t+1</sup> | Funktion  |

|---|------------------|-----------|

| 0 | q <sup>t</sup>   | speichern |

| 1 | $\frac{-}{q^t}$  | wechseln  |

- □ Ein synchrones Setzen oder Rücksetzen des T-Flipflops ist mit dem Eingang e nicht möglich.

- Um das Flipflop in einen definierten Grundzustand zu bringen, ist daher ein zusätzlicher Setz- oder Rücksetzeingang notwendig.

© 2010 Burkhard Stiller

M4 - 57

# Zusammenfassung

- RS-Flipflop (asynchron): r=s=1 verboten

→ RS-Latch (getaktet, pegelgesteuert)

- □ D-Flipflop, D-Latch: r und s =0 immer beachtet

- Taktflankengesteuertes D-Flipflop durch Zusammenschaltung zweier D-Latches

- □ JK-Flipflop: r und s = 1  $\rightarrow$  Ausgang komplementieren

- □ T-Flipflop: Eingang 1 → Ausgang komplementieren, sonst speichern

# Wichtige Hilfsmittel: Ansteuertabellen

| qt    | q <sup>t+1</sup> | r | S | RS-Flipflop |            | $q^{t}$        | q <sup>t+1</sup> | d |   |

|-------|------------------|---|---|-------------|------------|----------------|------------------|---|---|

| 0     | 0                | - | 0 |             |            | 0              | 0                | 0 |   |

| 0     | 1                | 0 | 1 |             |            | 0              | 1                | 1 |   |

| 1     | 0                | 1 | 0 |             |            | 1              | 0                | 0 |   |

| 1     | 1                | 0 | - |             | D-Flipflop | 1              | 1                | 1 |   |

|       |                  |   |   |             |            |                | ·                | I |   |

| $q^t$ | $q^{t+1}$        | j | k | JK-Flipflop | _          | q <sup>t</sup> | q <sup>t+1</sup> | е | - |

| 0     | 0                | 0 | - | -           |            | 0              | 0                | 0 |   |

| 0     | 1                | 1 | - |             |            | 0              | 1                | 1 |   |

| 1     | 0                | _ | 1 |             |            | 1              | 0                | 1 |   |

| 1     | 1                | _ | 0 |             | T-Flipflop | 1              | 1                | 0 |   |

© 2010 Burkhard Stiller

M4 - 59

## **Modul 4: Schaltwerke**

- □ Formale Grundlagen

- Endliche Automaten

- Asynchrone Schaltwerke, Flip-Flops

- Synchrone Schaltwerke

- □ Register-Transfer-Ebene

- □ Spezielle Schaltwerke

- Register, Zähler, Schieberegister

# **Entwurf synchroner Schaltwerke**

- Die Vorgehensweise beim Entwurf synchroner Schaltwerke soll ebenfalls an einem Beispiel erläutert werden.

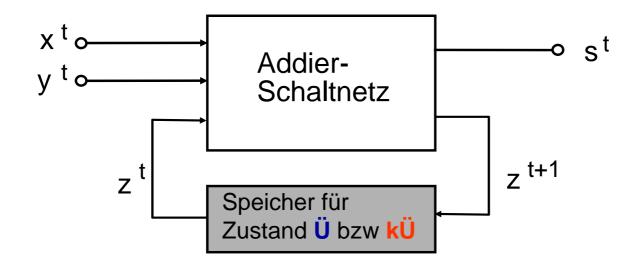

- Beispiel: Serienaddierer

- Zwei beliebig lange Dualzahlen sollen stellenweise addiert werden.

- Die Addition beginnt mit der Stelle niedrigster Wertigkeit.

- In jeder nachfolgenden Stelle muß der Übertrag der vorhergehenden Stelle berücksichtigt werden.

- Die Zahlen werden bitweise eingegeben, pro Taktschritt eine Stelle.

- Die Ausgabe soll ebenfalls bitweise erfolgen, wobei die Ausgabefolge zu jedem Zeitpunkt die Summe der bisherigen Eingabefolgen (ohne Übertrag) darstellt.

1001101001 + 1010011010 10100000011 617 + 666 = 1283

- später mehr

zur Rechnerarithmetik!

© 2010 Burkhard Stiller

M4 – 61

# Grundsätzliche Vorgehensweise

Ausgangsbasis: verbale Aufgabenstellung

- 1. Zusammenstellung der Ein- und Ausgabevariablen

- 2. Festlegung der Zustände

- 3. Entwerfen des Automatengraphen

- 4. Aufstellen einer Automatentafel

- 5. Wahl der Zustandskodierung

- 6. Erzeugung der kodierten Ablauftabelle

- 7. Erweiterung der Ablauftabelle um Flipflops

- 8. Minimierung der Ausgangs- und Ansteuernetze der Flipflops

- 9. Schaltwerk zeichnen

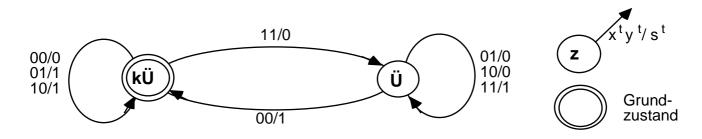

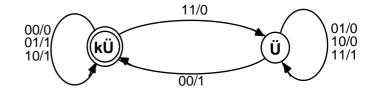

# Aufstellen des Automatengraphen

- Beispiel des Serienaddierers:

Zwei Eingabevariablen-Folgen, eine Zahl x und eine Zahl y, sowie eine Folge von Ausgabewerten, die Summe s.

- □ In einem gegebenen Takt muß von der Vorgeschichte des Schaltwerks lediglich der Übertrag aus dem vorhergehenden Takt bekannt sein.

- □ Demnach reichen zwei Zustände aus:

- Zustand Ü: Wird in dem Fall eingenommen, daß ein Übertrag aus der vorhergehenden Stelle zu berücksichtigen ist

- Zustand kÜ: Repräsentiert den anderen Fall (kein Übertrag)

© 2010 Burkhard Stiller

M4 - 63

### Blockschaltbild des Serienaddierers

Eingabe: x und y Ausgabe: s

Zustandsspeicher für Ü bzw. kÜ

## **Automatengraph**

- □ Es ist ein Mealy-Schaltwerk nötig, da die Ausgabe von den aktuellen Werten der Eingabevariablen abhängen soll.

- □ Im Automatengraphen werden deshalb die Ausgabebelegungen an die Kanten geschrieben.

- Automatengraph des Serienaddierers:

© 2010 Burkhard Stiller

M4 - 65

#### Aufstellen der Automatentafel

Aus dem Automatengraphen läßt sich die Automatentafel ableiten.

Automatentafel des Serienaddierers:

|    | z + /s |       |       |      |  |

|----|--------|-------|-------|------|--|

| Z  | x y =  |       |       |      |  |

|    | 00     | 01    | 10    | 11   |  |

| kÜ | kÜ /0  | kÜ /1 | kÜ /1 | Ü /0 |  |

| Ü  | kÜ /1  | Ü/0   | Ü /0  | Ü/1  |  |

|    |        |       |       |      |  |

Bei synchronen Schaltwerken werden stabile Zustände nicht gesondert markiert, da angenommen wird, daß alle Zustände bis zum nächsten Taktzyklus stabil sind.

## Wahl der Zustandskodierung

- □ Bei asynchronen Schaltwerken:

- Zustandskodierung sehr kritisch

- Wahl einer geeigneten Zustandskodierung ist für das Funktionieren des Schaltwerks entscheidend

- □ Bei synchronen Schaltwerken:

- Zustandskodierung unkritisch

- Ein synchrones Schaltwerk funktioniert grundsätzlich mit jeder eindeutigen Zustandskodierung

- Eine gute Zustandskodierung kann bei synchronen

Schaltwerken jedoch den Schaltungsaufwand reduzieren

- Zustandskodierung minimaler Länge bei k Zuständen:

© 2010 Burkhard Stiller M4 – 67

<u>ifi</u>

## Zustandskodierung beim Serienaddierer

- □ Zustandskodierung trivial, da nur zwei Zustände Ü und kÜ

- → Nur eine Zustandsvariable ü

| Z  | ü |

|----|---|

| kÜ | 0 |

| Ü  | 1 |

- □ Erzeugen der Ausgabe- und Übergangs-Schaltnetze:

- Einsetzen der Zustandskodierung in die Automatentafel

- → Kodierte Ablauftabelle des Schaltwerks

#### **Kodierte Ablauftabelle**

üt

0

| Z  | ü |                   |

|----|---|-------------------|

| kÜ | 0 | Zustandskodierung |

| Ü  | 1 |                   |

|    | z+/s  |      |      |     |  |

|----|-------|------|------|-----|--|

| Z  | x y = |      |      |     |  |

|    | 00    | 01   | 10   | 11  |  |

| kÜ | kÜ/0  | kÜ/1 | kÜ/1 | Ü/0 |  |

| Ü  | kÜ/1  | Ü/O  | Ü/0  | Ü/1 |  |

|    |       |      |      |     |  |

| kÜ≺ | 0 | 0 | 1 | 0 |

|-----|---|---|---|---|

|     | 0 | 1 | 0 | 0 |

|     | 0 | 1 | 1 | 1 |

| Ü≺  | 1 | 0 | 0 | 0 |

|     | 1 | 0 | 1 | 1 |

|     | 1 | 1 | 0 | 1 |

|     | 1 | 1 | 1 | 1 |

0

0

Automatentafel

Kodierte Ablauftabelle

ü<sup>t+1</sup>

0

$\mathbf{S}^{\mathsf{t}}$

0

1

0

0

0

1

© 2010 Burkhard Stiller

M4 - 69

#### ifi

## **Anmerkungen**

- Aus der kodierten Ablauftabelle lassen sich bereits die Funktionsausdrücke der Ausgabeschaltnetze ableiten

- Zur Erzeugung der Schaltnetze der Überführungsfunktion muß zuvor noch der verwendete Flipflop-Typ festgelegt werden

- Jeder Flipflop-Typ muß anders angesteuert werden

- Die Wahl eines Flipflop-Typs beeinflußt die Größe der Überführungsschaltnetze.

- □ Auch die Güte einer Zustandskodierung kann nur im Hinblick auf einen bestimmten Flipflop-Typ beantwortet werden.

# Wahl des Flipflop-Typs

- □ Der Serienaddierer soll mit JK-Flipflop realisiert werden.

- □ Ansteuertabelle des JK-Flipflops:

| q <sup>t</sup> | q <sup>t+1</sup> | j | k |

|----------------|------------------|---|---|

| 0              | 0                | 0 | - |

| 0              | 1                | 1 | - |

| 1              | 0                | - | 1 |

| 1              | 1                | - | 0 |

© 2010 Burkhard Stiller

M4 - 71

# **Ansteuerung des Flipflops**

□ Kodierte Ablauftabelle wird um die Ansteuereingänge des Flipflops erweitet:

| qt | q <sup>t+1</sup> | j | k |

|----|------------------|---|---|

| 0  | 0                | 0 | - |

| 0  | 1                | 1 | - |

| 1  | 0                | - | 1 |

| 1  | 1                | - | 0 |

| ü <sup>t</sup> | $\mathbf{x}^{t}$ | y <sup>t</sup> | ü <sup>t+1</sup> | s <sup>t</sup> | jt | k <sup>t</sup> |

|----------------|------------------|----------------|------------------|----------------|----|----------------|

| 0              | 0                | 0              | 0                | 0              | 0  | -              |

| 0              | 0                | 1              | 0                | 1              | 0  | -              |

| 0              | 1                | 0              | 0                | 1              | 0  | -              |

| 0              | 1                | 1              | 1                | 0              | 1  | -              |

| 1              | 0                | 0              | 0                | 1              | -  | 1              |

| 1              | 0                | 1              | 1                | 0              | -  | 0              |

| 1              | 1                | 0              | 1                | 0              | _  | 0              |

| 1              | 1                | 1              | 1                | 1              | _  | 0              |

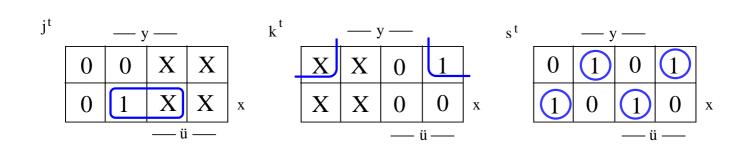

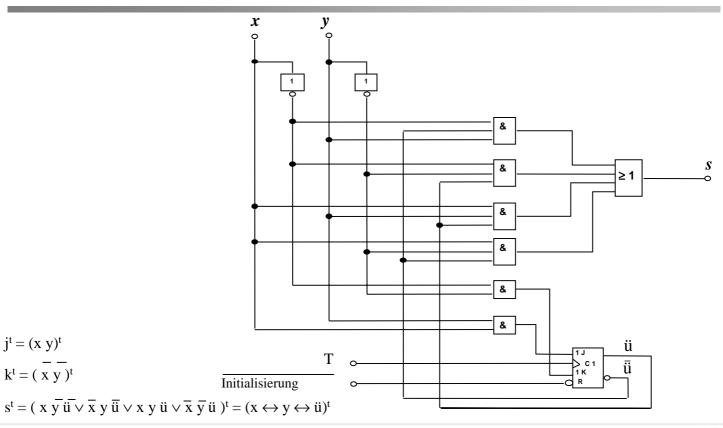

## Minimierte Ausgangs- und Ansteuernetze

$$\begin{split} & j^t = (x \ y)^t \\ & k^t = (\ \overline{x} \ \overline{y}\ )^t \\ & s^t = (\ x \ \overline{y} \ \overline{\ddot{u}} \lor \overline{x} \ y \ \overline{\ddot{u}} \lor x \ y \ \ddot{u} \lor \overline{x} \ \overline{y} \ \ddot{u} \ )^t = (x \leftrightarrow y \leftrightarrow \ddot{u})^t \end{split}$$

© 2010 Burkhard Stiller

M4 - 73

#### <u>ifi</u>

## Realisierung des Serienaddierers

#### Modul 4: Schaltwerke

- Formale Grundlagen

- Endliche Automaten

- Asynchrone Schaltwerke, Flip-Flops

- Synchrone Schaltwerke

- Register-Transfer-Ebene

- Spezielle Schaltwerke

- Register, Zähler, Schieberegister

© 2010 Burkhard Stiller

M4 - 75

#### ifi

## Register-Transfer-Ebene

- Für den Entwurf komplexerer Systeme erweist es sich als notwendig, vom detaillierten Verhalten konkreter Bausteine zu abstrahieren.

- Übergang von der Beschreibung der Schaltung auf der Gatterebene zu einer Beschreibung auf der sogenannten Register-Transfer-Ebene (RT-Ebene)

- Grundelemente der RT-Ebene:

- Register zur Speicherung der zu verarbeitenden Daten

- Funktionale Einheiten, wie Z\u00e4hler, Addierer, Multiplexer und Demultiplexer, mit denen die Verarbeitung durchgef\u00fchrt werden kann.

- Die Einheit des Informationsflusses zwischen diesen Elementen ist das Datenwort, das eine feste Anzahl zusammengehörender Bits umfaßt.

- Die zu verarbeitenden Daten sind oft also keine einzelnen Bits, sondern Bit-Gruppen oder Bitvektoren.

## Komponenten zur Realisierung spezieller Funktionen der RT-Ebene

| Тур         | Komponente                                                           | Funktion                                       |

|-------------|----------------------------------------------------------------------|------------------------------------------------|

| Schaltnetze | Wortverknüpfung                                                      | Boolesche Operation                            |

|             | Multiplexer (MUX)                                                    | Datenübertragung, allg.<br>Funktionen          |

|             | Kodierer/Dekodierer                                                  | Codeprüfung, Codewandlung                      |

|             | Programmierbare Matrizen (PLA)                                       | Allgemeine Funktionen                          |

|             | Arithmetische Elemente (Addierer, arithmetisch-Logische Einheit ALU) | Numerische Operationen                         |

| Schaltwerke | Register                                                             | Informationsspeicherung                        |

|             | Schieberegister                                                      | Serien-/Parallel-Umwandlung                    |

|             | Zähler                                                               | Erzeugung von Steuer-<br>und Zeitgebersignalen |

Multiplexer und PLA-Bausteine sind funktional vollständig, d.h. sie sind zusammen mit Registern für den Entwurf eines allgemeinen Schaltwerks ausreichend.

© 2010 Burkhard Stiller

M4 - 77

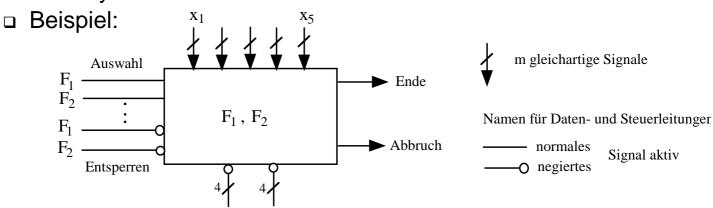

### Symbole auf der RT-Ebene

Als Schaltsymbole zur Kennzeichnung der Funktion eines Bausteins werden Kästen mit Funktionsangabe oder Normsymbole verwendet.

- Auswahlsignale:

- Legen fest, welche Funktion realisiert werden soll.

- Entsperrsignale:

- Definieren Zeitpunkt für den Beginn einer Operation oder erlauben deren Ablauf.

## **Beschreibung von RT-Operationen**

- □ Eine Beschreibung von Register-Transfer-Operationen enthält:

- Die Grobstruktur des Datenflusses zwischen den speichernden und den verarbeitenden Einheiten:

- Blockdiagramm, in dem Leitungsbündel Register und Funktionsbausteine miteinander verbinden oder

- Beschreibung mit einer Hardware-Beschreibungssprache wie z.B. VHDL oder VerilogHDL (HDL=Hardware Description Language).

© 2010 Burkhard Stiller

M4 - 79

## Register-Transfer-Anweisungen (1)

Als Basis zur Beschreibung von RT-Operationen dienen sogenannte Register-Transfer-Anweisungen in der Form:

$$Z \leftarrow F(X_1, X_2, ..., X_n)$$

Z, X<sub>1</sub>, X<sub>2</sub> ..., X<sub>n</sub> stellen Register dar.

F ist eine numerische oder Boolesche Funktion.

- □ Die Anweisung kann wie folgt interpretiert werden:

- Die Verknüpfung der Eingangsgrößen X<sub>1</sub>, X<sub>2</sub> ..., X<sub>n</sub> durch F liefert den Registerinhalt für Z in den nächsten Taktschritten.

## Register-Transfer-Anweisungen (2)

□ Eine Beeinflussung der Ausführung der Anweisung erfolgt durch eine Steuergröße c:

c:

$$Z \leftarrow F(X_1, X_2, ..., X_n)$$

oder

if (c=1) then

$$Z \leftarrow F(X_1, X_2, ..., X_n)$$

□ Die Anweisungen einer Register-Transfer-Sprache können durch Hardware-Komponenten interpretiert werden.

© 2010 Burkhard Stiller

M4 - 81

#### ifi

## **Beispiel**

#### Modul 4: Schaltwerke

- Formale Grundlagen

- Endliche Automaten

- Asynchrone Schaltwerke, Flip-Flops

- Synchrone Schaltwerke

- Register-Transfer-Ebene

- Spezielle Schaltwerke

- Register, Zähler, Schieberegister

© 2010 Burkhard Stiller

M4 - 83

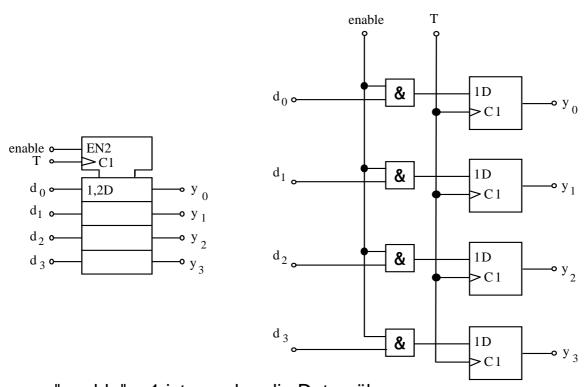

#### Register

- □ Lineare Anordnung von Flipflops zur Speicherung mehrerer Bits (Bitvektor).

- □ Die Flipflops werden mit einem gemeinsamen Takt angesteuert.

- □ Einfachstes Register:

- Unverkoppelt nebeneinandergesetzte D-Flipflops.

- Im allgemeinen werden die Flipflops durch zusätzliche gemeinsame Steuersignale beeinflußt.

# 4-Bit-Register aus D-Flipflops mit Freigabesignal

Nur wenn "enable" = 1 ist, werden die Daten übernommen.

© 2010 Burkhard Stiller

M4 - 85

#### ifi

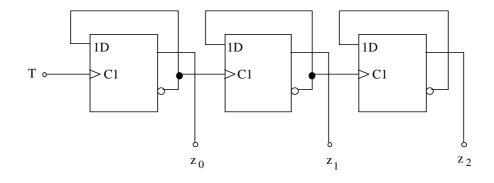

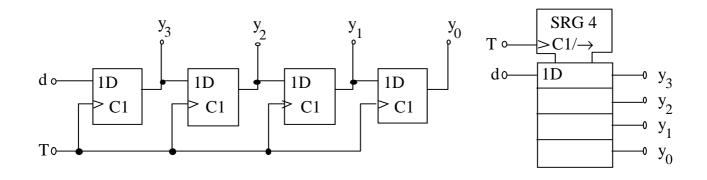

## Schieberegister (1)

- □ Kette von in Reihe geschalteten Registern oder D-Flipflops

- □ Der Ausgang eines Speicherelements ist jeweils mit dem Eingang des nächsten verbunden.

### Schieberegister (2)

#### Division/Multiplikation durch/mit 2

- □ Interpretiert man die Bitfolge y<sub>3</sub> y<sub>2</sub> y<sub>1</sub> y<sub>0</sub> als Dualzahl, entspricht ein Rechtsschieben (mit d = 0) einer Division durch 2 (ohne Rest).

- □ Schiebt man die Bitfolge ein Bit nach links (mit 0 als neuem letztem Bit), erhält man eine Multiplikation mit 2.

© 2010 Burkhard Stiller

M4 - 87

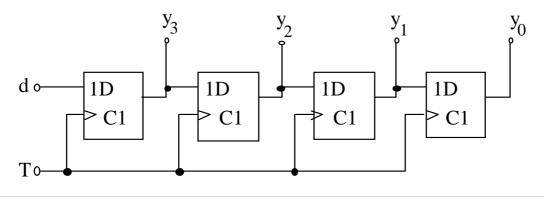

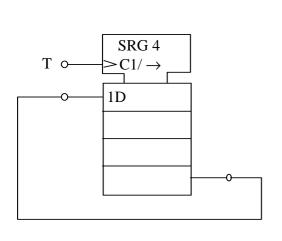

### Schieberegister (3)

#### Umlaufspeicher/Ringzähler

Verbindet man den seriellen Ausgang eines Schieberegisters mit seinem seriellen Eingang, erhält man einen Umlaufspeicher (Ringzähler), der eine Bitfolge beliebig lange zwischenspeichern kann und dabei im Kreise schiebt.

Umlaufspeicher mit Beispiel für umlaufenden Speicherinhalt

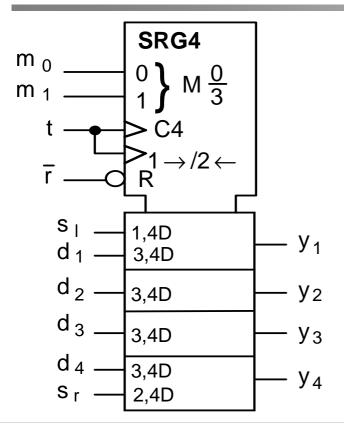

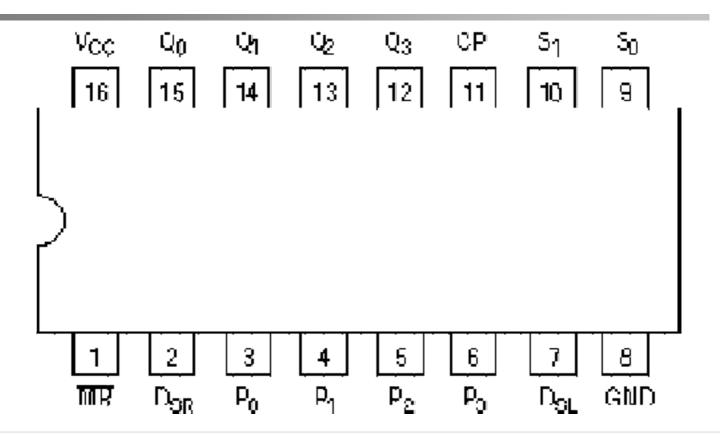

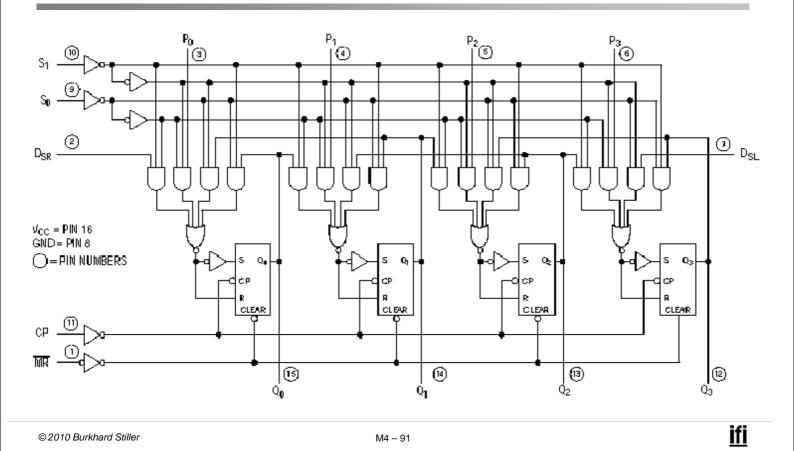

## Konkreter Baustein: 74LS194 (1)

#### **Funktionsmodi**

Daten, die an den 4 Paralleleingängen  $\mathbf{d}_1$  bis  $\mathbf{d}_4$  anliegen, werden parallel geladen.

Daten am Eingang werden  $\mathbf{s_l}$  seriell übernommen und die alten Registerinhalte nach unten weitergeschoben.

Daten am Eingang  $\mathbf{s_r}$  werden seriell übernommen und alte Registerinhalte nach oben weitergeschoben.

Die aktuellen Registerinhalte werden über mehrere Takte gespeichert.

Mit dem Rücksetz-Eingang rkann man das Schieberegister auch asynchron rücksetzen.

© 2010 Burkhard Stiller

M4 - 89

#### ifi

## Konkreter Baustein: 74LS194 (2)

## Konkreter Baustein: 74LS194 (3)

Zähler (1)

- □ Zähler erfüllen in digitalen Systemen mehrere Aufgaben:

- Man kann Impulse abzählen.

- Man kann aufeinanderfolgende Adressen eines Speichers adressieren (z.B. bei Programmzählern) oder aufeinanderfolgende Arbeitsschritte kontrollieren (bei Steuerwerken).

- □ Eine vorgegebene Impulsfolge läßt sich in der Frequenz reduzieren, der Zähler wirkt als Frequenzteiler. Dabei macht man sich die Tatsache zunutze, dass sich das Bit i einer Zahl z<sub>n</sub>...z<sub>i</sub>...z<sub>0</sub> nur 2<sup>-i</sup> mal so oft ändert wie Bit 0, wenn diese Zahl fortlaufend inkrementiert wird.

### Zähler (2)

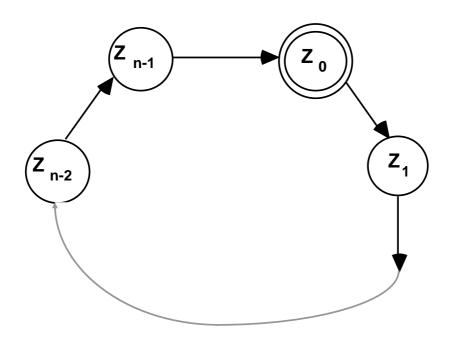

Grundlegendes Übergangsdiagramm

© 2010 Burkhard Stiller

M4 - 93

#### ifi

#### **Anmerkungen**

- Durch Modifizierung der Grundstruktur:

- → Setz- oder Rücksetzeingänge, Freigabeeingang oder eine Möglichkeit, vorwärts und rückwärts zu zählen.

- □ Sind die Zustände dual kodiert (Zustand Z<sub>i</sub> wird mit der Dualzahl i kodiert), liegt ein Dualzähler vor.

- Abhängig von der Länge n des Zählzyklus wird ein Zähler als Modulo-n-Zähler bezeichnet.

- $\square$  Ist n = 2<sup>m</sup>, so handelt es sich um einen m-stelligen Zähler.

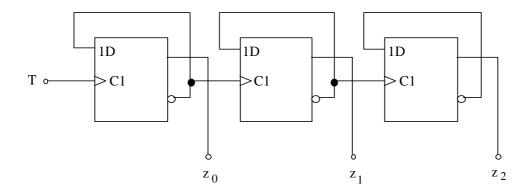

#### **Asynchrone Zähler**

- Die Größe des Ansteuerschaltnetzes wächst mit zunehmender Bitanzahl stark an.

- Aus diesem Grund sind asynchrone Zähler (engl.: ripple counter) attraktiv.

Realisierung eines asynchronen 3-stelligen Dualzählers

© 2010 Burkhard Stiller

M4 - 95

#### <u>ifi</u>

#### Nachteile asynchroner Zähler

- Diese Schaltung ist langsamer, da jedes Flipflop erst dann reagiert, wenn das vorhergehende Flipflop von 1 nach 0 umgeschaltet hat.

- Außerdem ändern sich die Ausgänge der Schaltung nicht gleichzeitig.